基于FPGA的自动升降电梯控制系统设计(VHDL)☆

无需注册登录,支付后按照提示操作即可获取该资料.

基于FPGA的自动升降电梯控制系统设计(VHDL)☆(任务书,开题报告,中期检查报告表,毕业论文,25000字,程序)

摘 要

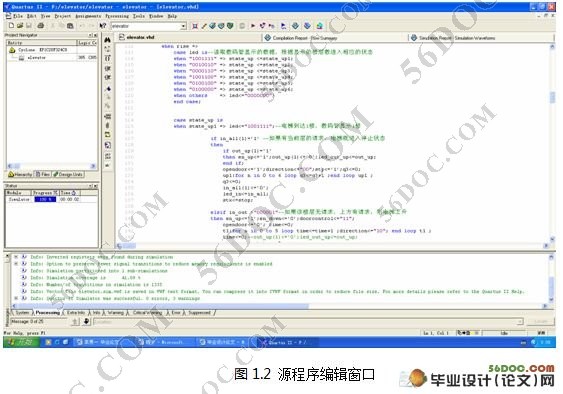

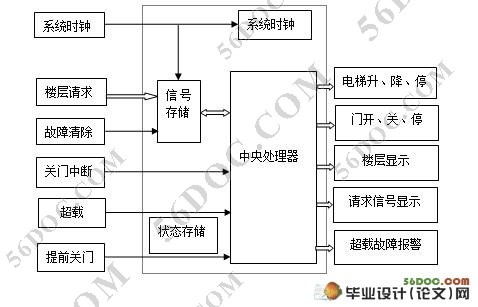

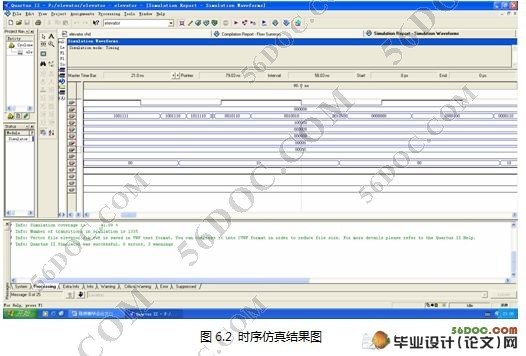

该设计是一个基于FPGA的自动升降电梯控制系统。它的设计是采用VHDL硬件描述语言使用EDA技术在Quartus II软件平台上设计完成的,调试并且时序仿真通过后再下载到开发板上调试通过。这个系统分为4个模块:外部数据采集模块、信号存储模块、中央处理控制模块、信号显示模块。中央处理模块采用状态机的方式来完成的。电梯的运行和停止过程包括8个状态:上升、下降、停止、开门、关门、等待、超载以及故障。其中上升和下降过程又分别包含1到6楼六个子状态。通过不同条件的改变来控制状态之间的变换。这些条件的改变是通过对一些输入输出和寄存器信号的变化来完成的。这些信号包括每个楼层的上升、下降、楼层请求、运动方向显示、楼层显示等信号。所以设计了数据采集和存储模块来采集并存储这些信号。信号显示模块的设计体现在电梯每进入一种状态就会有相应的输出和显示。

关键词:Quartus II,FPGA,VHDL,状态机

ABSTRACT

The design is an FPGA-based control system for automatic elevators.It is designed using VHDL hardware description language and the technology of EDA,and employing Quartus II EDA software platform to design , debugging, and timing simulation and then downloaded to the development board for debugging.The system is divided into four modules: external data acquisition module, signal storage module, a central processing control module, the signal display module.Central processing module uses the state machine approach to completion.The elevator 's process of operation and stop the includes eight states: up, down, stop, open, closed, waiting, overload and breakdown.Inside,Rise and fall states also contain 1-6 floor six sub-state.The changes of different conditions result in the transformation among the state.Changes of these conditions is resulted from a number of input or output or register signal convert .These signals include the rise or fall of each floor, floor request, the motion direction display, floor display signal and so on.Therefore the data collection and storage module is designed to collect and store these signals.Signal display module designed is embodied that if the elevator enter into a state ,there will be corresponding outputs and displays.

Keywords: Quartus II, VHDL, FPGA, state machine

电梯控制系统总体设计

该电梯控制系统的设计包括四个模块:外部信号高速采集模块、信号存储模块、中央处理控制模块、信号显示模块。

外部信号高速采集模块和存储模块的设计需求。外部用户的请求包括:电梯外部1楼到5楼的上升请求,2到6楼的下降请求,电梯内部1到6楼的请求。提前开门、延时关门开关。这些信号的检测是通过时钟信号的触发完成的,所以要及时得将这些信号采集并存储好。所以需要定义一些寄存器信号单元来存储这些请求数据。

中央处理控制模块的设计需求。它的主要功能是:(1)完成六个楼层多用户的载客服务控制;(2)电梯运行时显示电梯的运行方向和所在的楼层;(3)当电梯到达选择的楼层时,电梯自动开门;(4)具有提前关门和延时关门的功能;(5)响应分控器的有效请求,如果到达有请求的楼层,电梯自动开门。所以在这个模块的设计过程中需要设计电梯的运行方向和所在楼层的显示信号,开关门使能信号,提前关门和延时关门信号,上升下降使能信号,超载、故障等报警信号等等。

信号显示模块设计需求。结合电梯的基本功能,需要显示给外界用户看的信号有:电梯内和电梯外上升下降的请求信号、到达的楼层数信号,电梯的运动方向,电梯门的开与关信号等等。

硬件需求:

1.CPU:Interl(R) Pentium(R)1.60GHz

2.内存:256MB及以上

3. Create-FPGA/SOPC-EB实验开发箱

4. Create-FPGA/SOPC-EB开发板和核心主板

1.5.2 软件需求:

1.操作系统版本:Windows XP /2003Server

2.Quartus II 6.0

#p#副标题#e#

目 录

摘 要 I

ABSTRACT II

第1章 绪 论 1

1.1 课题来源 1

1.2 开发背景 1

1.3 开发环境 2

1.3.1 Quartus II 6.0集成开发环境 2

1.3.2 硬件环境:Create-FPGA/SOPC-EB开发板(增强版) 4

1.4 相关技术介绍 6

1.4.1 关于VHDL语言 6

1.4.2 关于EDA技术 6

1.4.3 关于FPGA 7

1.4.4 关于状态机 8

1.4.5 硬件测试技术 9

1.5 系统软硬件需求 9

1.5.1 硬件需求: 9

1.5.2 软件需求: 9

第2章 系统分析 10

2.1 系统需求 10

2.1.1 需求分析 10

2.1.2 可行性分析 11

2.1.3 设计目标 12

2.2 系统功能模块需求 12

第3章 系统总体结构分析 13

3.1 电梯控制系统总体设计 13

3.2 电梯状态转换设计 14

第4章 系统详细设计 16

4.1 系统总体设计规划 16

4.2 构造体内部模块结构设计 18

4.2.1 内部寄存器信号定义设计 18

4.2.2 信号输出显示 19

4.2.3 状态机的设计 20

第5章 常见硬件故障分析 28

5.1电源问题 28

5.2 逻辑错误 28

5.3 可靠性问题 29

5.4元器件失效 29

第6章 仿真结果 29

结 论 32

参考文献 34

附 录 35

致 谢 50